# Linux Synchronization Mechanism: spinlock

Adrian Huang | Dec, 2022

- \* Based on kernel 5.11 (x86\_64) QEMU

- \* 2-socket CPUs (4 cores/socket)

- \* 16GB memory

- \* Kernel parameter: nokaslr norandmaps

- \* KASAN: disabled

- \* Userspace: ASLR is disabled

- \* Legacy BIOS

#### Agenda

- Spinlock history Approach evolution

- ✓ Simple Approach: Spin on test-and-set

- √ Test and test-and-set (spin on read)

- ✓ Ticket spinlock

- ✓ MCS (Mellor-Crummey & Scott) lock

- ➤ Performance benchmark: Ticket spinlock vs MCS lock

- ➤ MCS Lock History in Linux Kernel

- Current spinlock approach in Linux kernel: qspinlock (Queue spinlock)

- spin\_lock() SMP & UP

- spin\_lock() API variants

- ✓ How to use those variants in different scenarios

- Spinlock derivative: rwlock and seqlock

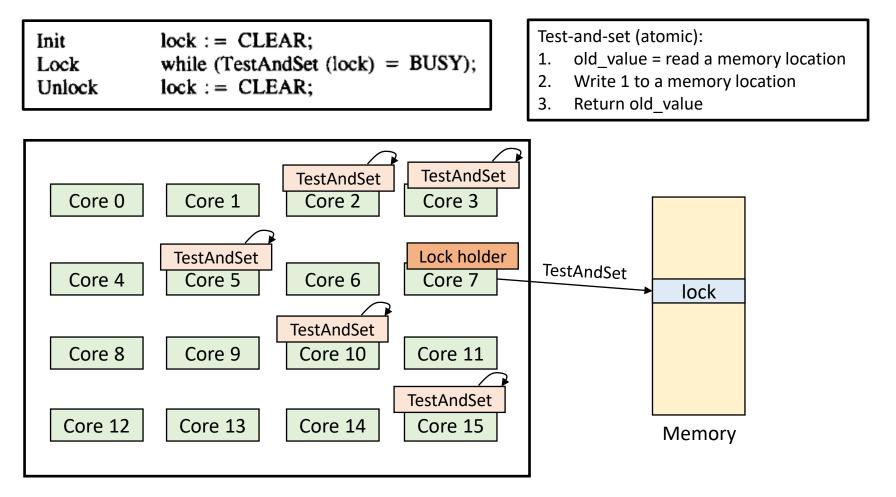

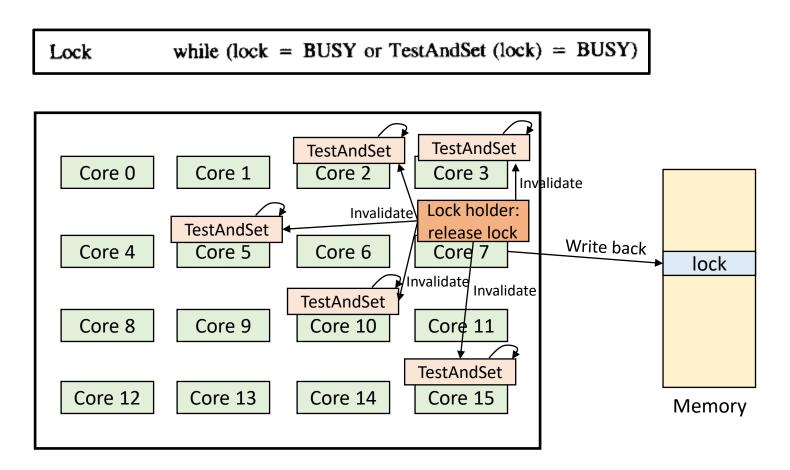

### Simple Approach: Spin on test-and-set

[Spinning Cores] Keep consuming memory bus (write 1): Cache coherence

#### Simple Approach: Spin on test-and-set

Init lock := CLEAR;

Lock while (TestAndSet (lock) = BUSY);

Unlock lock := CLEAR;

Test-and-set (atomic):

- 1. old\_value = read a memory location

- 2. Write 1 to a memory location

- 3. Return old value

- Read Invalidate message of MESI Protocol Messages

- ✓ Reference: C.2.2 MESI Protocol Messages of <u>Is Parallel Programming Hard</u>, And, If So, What Can You Do About It?

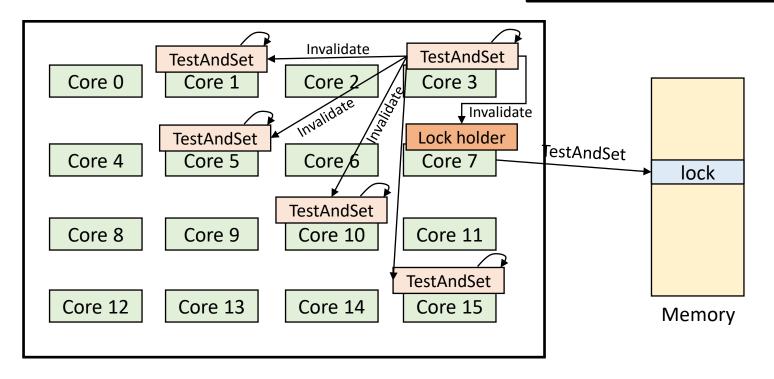

Due to the memory write, spinning cores invalidate cache copies of cores even if the value is not changed

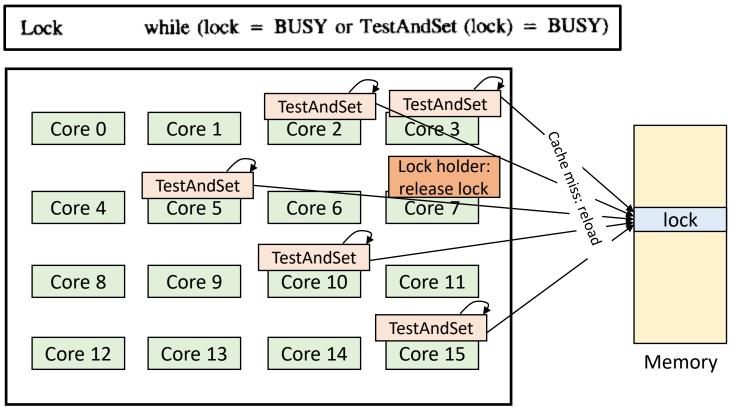

#### Simple Approach: Spin on test-and-set

Init lock := CLEAR;

Lock while (TestAndSet (lock) = BUSY);

Unlock lock := CLEAR;

Test-and-set (atomic):

- 1. old\_value = read a memory location

- 2. Write 1 to a memory location

- 3. Return old\_value

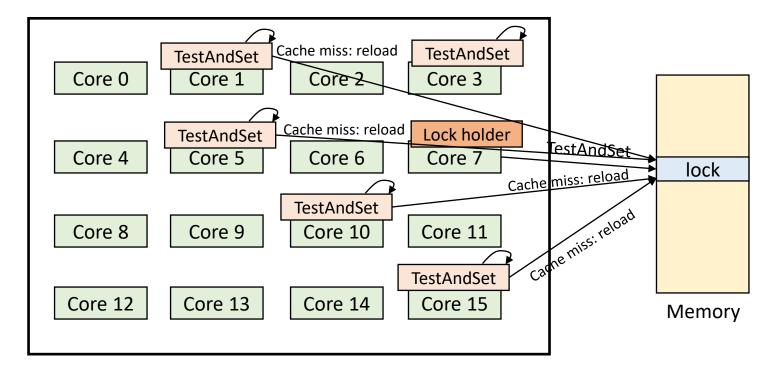

[Spinning Cores] Cores reload the memory due to the cache miss: performance impact

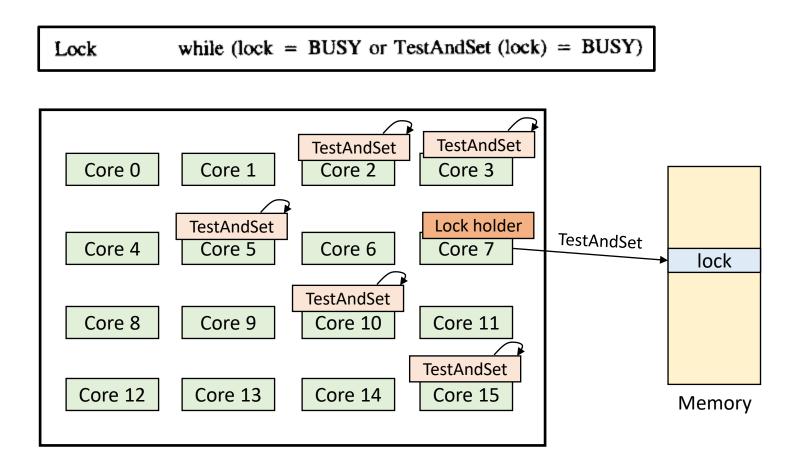

### Test and test-and-set (spin on read)

- 1. Spinning is done in the cache without consuming memory bus

- 2. Reduce the repeated test-and-set cost if the lock is held

### Test and test-and-set (spin on read)

- 1. Spinning is done in the cache without consuming memory bus

- 2. Reduce the repeated test-and-set cost if the lock is held

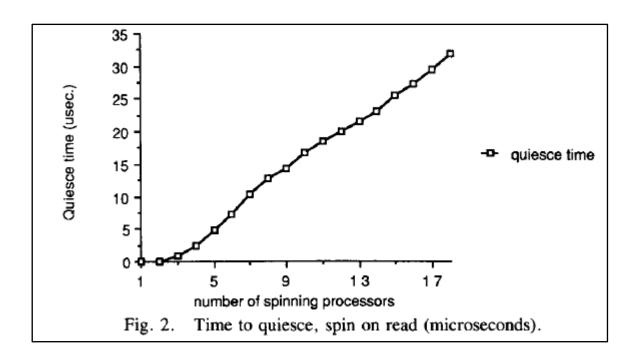

### Test and test-and-set (spin on read)

- 1. Spinning cores incur a read miss and fetch the new value back into cache

- 2. Spinning cores compete for accessing memory bus

- 3. The first core to test-and-set will acquire the lock

- 4. Other spinning cores cannot get lock: invalidate caches & cache misses

- Quiescence: These operations are finished

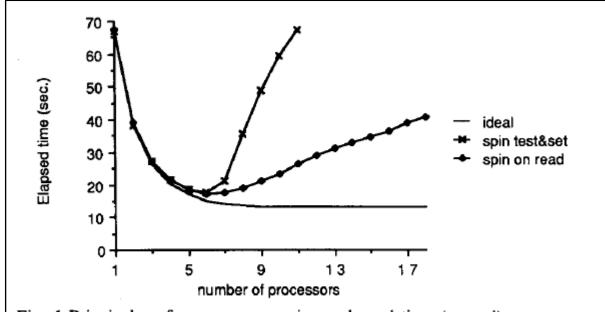

#### Performance Comparison

Fig. 1.Principal performance comparison: elapsed time (second) to execute benchmark (measured). Each processor loops one million/P times: acquire lock, do critical section, release lock, and compute.

Reference from: T. E. Anderson, "The performance of spin lock alternatives for shared-money multiprocessors", IEEE Transactions on Parallel and Distributed Systems, vol. 1, no. 1, pp. 6-16, 1990.

# Issue Statements about "Spin on test-and-set" and "Test and test-and-set"

- Cache coherence

- ✓ [Cache-line bouncing] Scalability issue

- All spinning cores compete the lock when the lock is freed by lock holder

- ✓ Unfairness

- > Ticket spinlock is proposed to fix the unfairness

#### Ticket spinlock (v2.6.25: released in April 2008)

#### **Concept: pseudo code**

#### commit 314cdbefd1fd0a7acf3780e9628465b77ea6a836

Author: Nick Piggin <npiggin@suse.de>

Date: Wed Jan 30 13:31:21 2008 +0100

x86: FIFO ticket spinlocks

Introduce ticket lock spinlocks for x86 which are FIFO. The implementation is described in the comments. The straight-line lock/unlock instruction sequence is slightly slower than the dec based locks on modern x86 CPUs, however the difference is quite small on Core2 and Opteron when working out of cache, and becomes almost insignificant even on P4 when the lock misses cache. trylock is more significantly slower, but they are relatively rare.

On an 8 core (2 socket) Opteron, spinlock unfairness is extremely noticable, with a userspace test having a difference of up to 2x runtime per thread, and some threads are starved or "unfairly" granted the lock up to 1 000 000 (!) times. After this patch, all threads appear to finish at exactly the same time.

The memory ordering of the lock does conform to x86 standards, and the implementation has been reviewed by Intel and AMD engineers.

The algorithm also tells us how many CPUs are contending the lock, so lockbreak becomes trivial and we no longer have to waste 4 bytes per spinlock for it.

After this, we can no longer spin on any locks with preempt enabled and cannot reenable interrupts when spinning on an irq safe lock, because at that point we have already taken a ticket and the would deadlock if the same CPU tries to take the lock again. These are questionable anyway: if the lock happens to be called under a preempt or interrupt disabled section, then it will just have the same latency problems. The real fix is to keep critical sections short, and ensure locks are reasonably fair (which this patch does).

Signed-off-by: Nick Piggin <npiggin@suse.de>

Signed-off-by: Thomas Gleixner <tglx@linutronix.de>

Signed-off-by: Ingo Molnar <mingo@elte.hu>

### Ticket spinlock (v2.6.25: released in April 2008)

#### **Concept: pseudo code**

```

struct spinlock_t {

int current_ticket;

int next_ticket;

};

void spin_lock(spinlock_t *lock)

{

int t = atomic_fetch_and_inc(&lock->next_ticket);

while (t != lock ->current_ticket)

; /* spin */

}

void spin_unlock(spinlock_t *lock)

{

lock ->current_ticket++;

}

```

#### v2.6.25 implementation

```

Commit 3a556b26a2718e48aa2b6ce06ea4875ddcd0778e

Author: Nick Piggin <npiggin@suse.de>

Date: Wed Jan 30 13:33:00 2008 +0100

x86: big ticket locks

This implements ticket lock support for more than 255 CPUs on x86. The code gets switched according to the configured NR_CPUS.

Signed-off-by: Nick Piggin <npiggin@suse.de>

Signed-off-by: Ingo Molnar <mingo@elte.hu>

Signed-off-by: Thomas Gleixner <tglx@linutronix.de>

```

```

typedef struct arch_spinlock {

unsigned int slock;

} arch_spinlock_t;

arch/x86/include/asm/spinlock_types.h

```

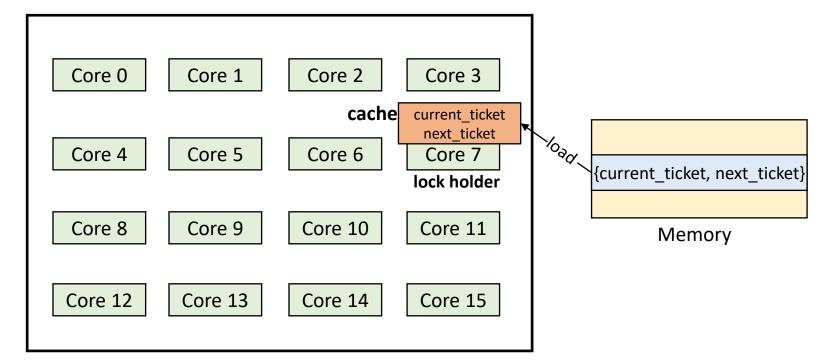

#### Ticket spinlock: Acquire a spinlock

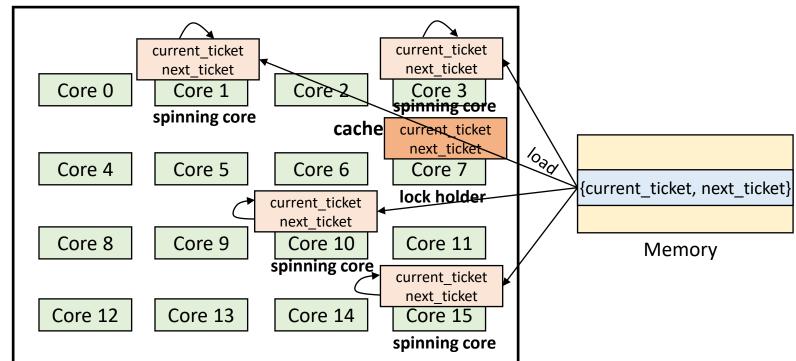

Ticket spinlock: Other cores acquire a locked spinlock

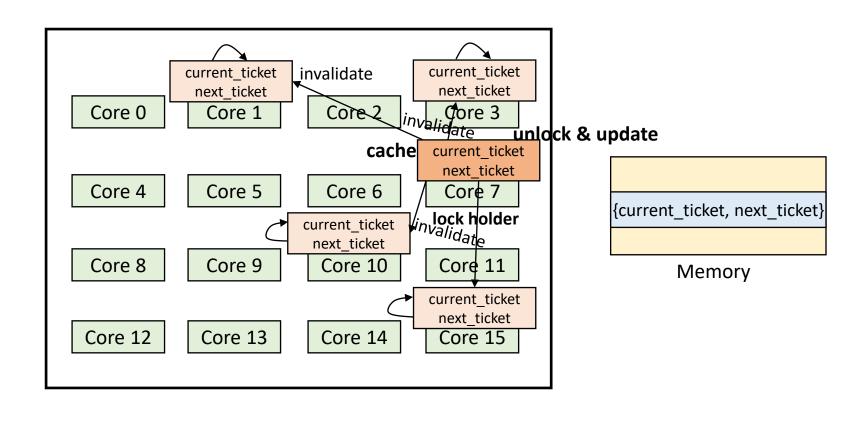

Ticket spinlock: Lock holder unlocks a spinlock and accumulates current ticket

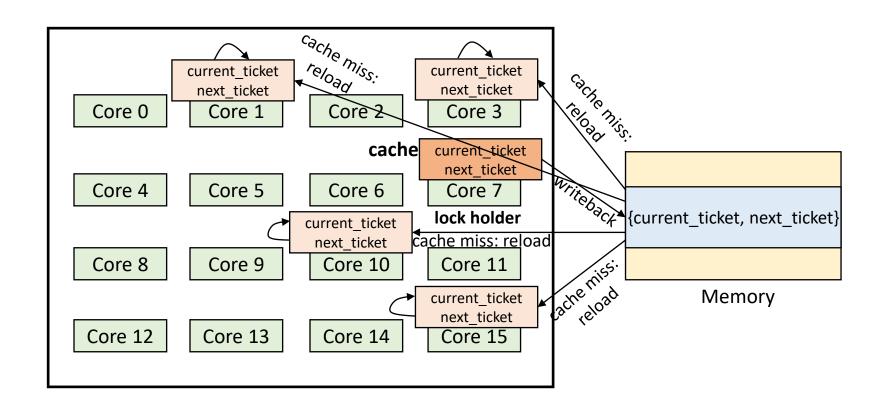

## Ticket spinlock: Cache miss → Reload

[Ticket spinlock] Cache coherence issue: non-scalable spinlock (Cache-line bouncing)

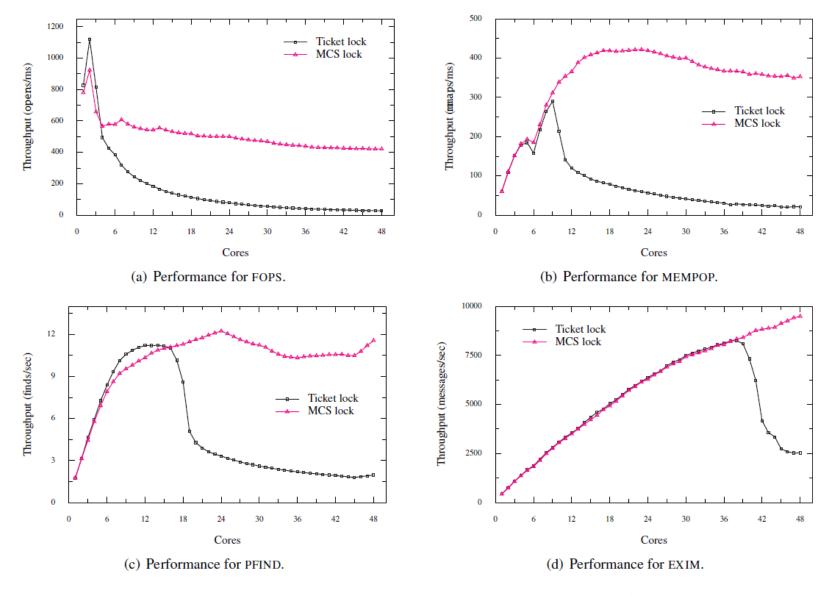

#### Ticket spinlock: Performance Measurement

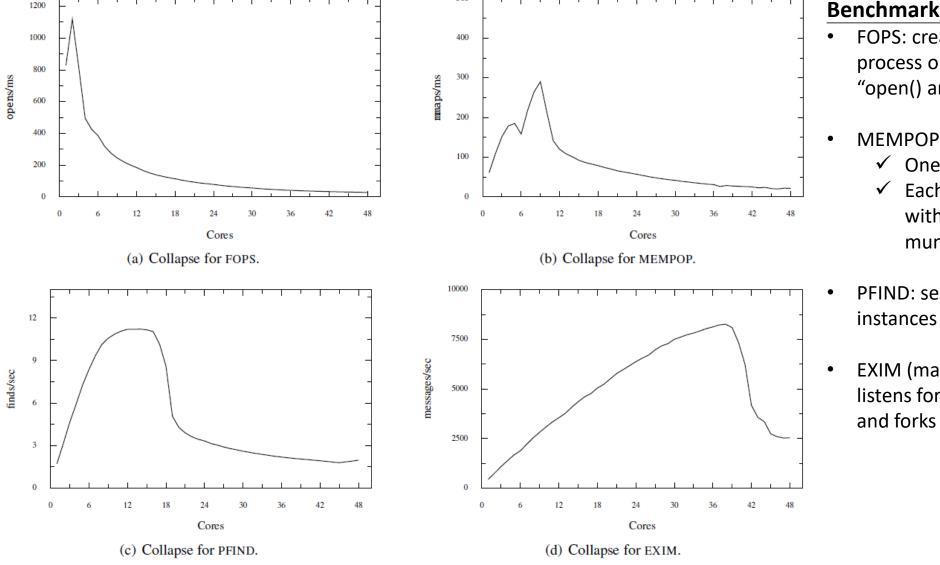

**Benchmarks**

- FOPS: creates a single file and starts one process on each core. Repeated system calls "open() and close()".

- - ✓ One process per core

- Each process mmaps 64 kB of memory with the MAP POPULATE flag, then munmaps the memory

- PFIND: searches for a file by executing several instances of the GNU find utility

- EXIM (mail server): A single master process listens for incoming SMTP connections via TCP and forks a new process for each connection

Figure 2: Sudden performance collapse with ticket locks.

Reference Paper: Boyd-Wickizer, Silas, et al. "Non-scalable locks are dangerous." Proceedings of the Linux Symposium. 2012.

#### Ticket spinlock: Performance Measurement

| Benchmark | Operation time<br>(cycles) | Top lock instance name | Acquires per operation | Average critical section time (cycles) | % of operation in critical section |

|-----------|----------------------------|------------------------|------------------------|----------------------------------------|------------------------------------|

| FOPS      | 503                        | d_entry                | 4                      | 92                                     | 73%                                |

| MEMPOP    | 6852                       | anon_vma               | 4                      | 121                                    | 7%                                 |

| PFIND     | 2099 M                     | address_space          | 70 K                   | 350                                    | 7%                                 |

| EXIM      | 1156 K                     | anon_vma               | 58                     | 165                                    | 0.8%                               |

Figure 3: The most contended critical sections for each Linux microbenchmark, on a single core.

```

struct mcs_spinlock {

struct mcs_spinlock *next;

int locked; /* 1 if lock acquired */

int count; /* nesting count, see qspinlock.c */

};

kernel/locking/mcs_spinlock.h

```

#### **MCS Lock**

- Adhere to fairness: FIFO (Implemented via linked list)

- Scalable spinlock: Prevent cache coherence issue

- ✓ Each core reference its own data 'next' (struct mcs\_spinlock)

- Data ownership concept: Is Parallel Programming Hard, And, If So, What Can You Do About It?

```

struct mcs_spinlock {

struct mcs_spinlock *next;

int locked; /* 1 if lock acquired */

int count; /* nesting count, see qspinlock.c */

};

kernel/locking/mcs_spinlock.h

```

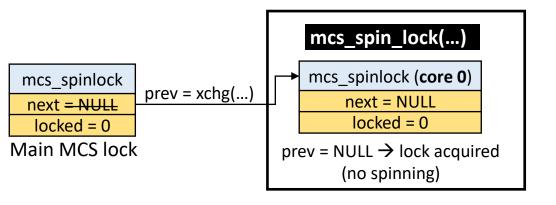

```

void mcs spin lock(struct mcs spinlock **lock, struct mcs spinlock *node)

struct mcs_spinlock *prev;

/* Init node */

node -> locked = 0;

node->next = NULL;

lines: We rely on the full barrier with global transitivity

prev = xchg(lock, node);

if (likely(prev == NULL)) {

* Lock acquired, don't need to set node->locked to 1. Threads

* only spin on its own node->locked value for lock acquisition.

* However, since this thread can immediately acquire the lock

* and does not proceed to spin on its own node->locked, this

* value won't be used. If a debug mode is needed to

* audit lock status, then set node->locked value here.

return;

WRITE ONCE (prev->next, node);

/* Wait until the lock holder passes the lock down. */

arch mcs spin lock contended(&node->locked);

kernel/locking/mcs spinlock.h

62,8

```

- 1. Adhere to fairness

- 2. Scalable spinlock: Prevent cache coherence issue

```

void mcs spin lock(struct mcs spinlock **lock, struct mcs spinlock *node)

struct mcs spinlock {

struct mcs_spinlock *next;

struct mcs spinlock *prev;

int locked; /* 1 if lock acquired */

/* Init node */

int count; /* nesting count, see gspinlock.c */

node->locked = 0:

};

node->next = NULL;

kernel/locking/mcs spinlock.h

prev = xchg(lock, node);

if (likely(prev == NULL)) {

* Lock acquired, don't need to set node->locked to 1. Threads

* only spin on its own node->locked value for lock acquisition

* However, since this thread can immediately acquire the lock

* and does not proceed to spin on its own node->locked, this

* value won't be used. If a debug mode is needed to

* audit lock status, then set node->locked value here.

return;

WRITE ONCE(prev->next, node);

/* Wait until the lock holder passes the lock down. */

arch mcs spin lock contended(&node->locked);

kernel/locking/mcs spinlock.h

62,8

prev = xchg(...)

mcs_spin_lock(...)

prev

mcs spinlock (core 1)

mcs spinlock (core 0)

mcs spinlock

next = NULL

next = NULL

next

Spinning until

Will be replaced by

WRITE ONCE(prev->next, node)

locked = 0

locked = 0

locked = 0

locked = 1

xchg()

```

1. [Spinning core] check its owner `locked`

lock acquired (no spinning)

Main MCS lock

2. 'next' pointer of the main MCS lock indicates the tail of the queue of waiting cores

3 prev!= NULL → locked by another core

```

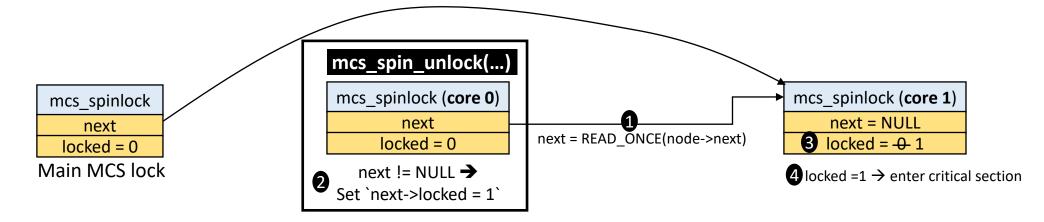

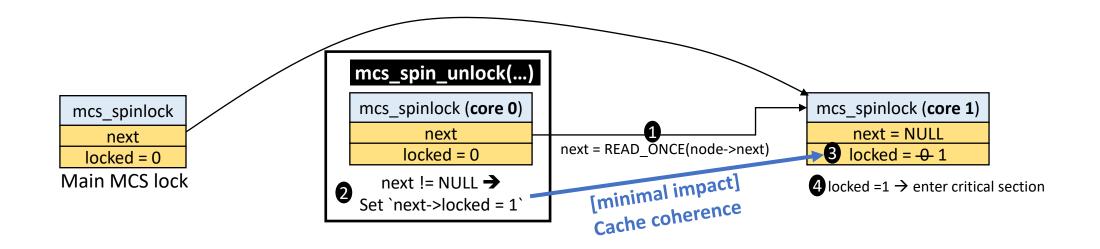

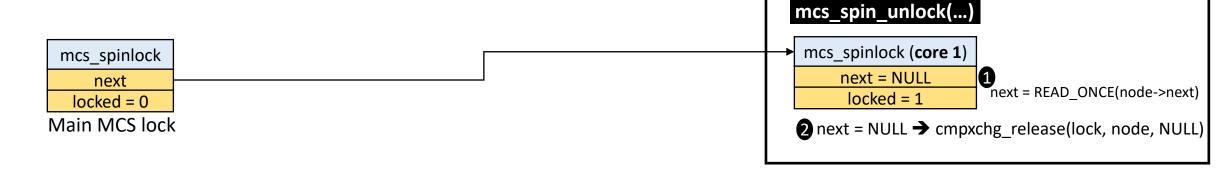

static inline

void mcs spin unlock(struct mcs spinlock **lock, struct mcs spinlock *node)

struct mcs_spinlock *next = READ_ONCE(node->next);

if (likely(!next)) {

* Release the lock by setting it to NULL

if (likely(cmpxchg release(lock, node, NULL) == node))

return;

/* Wait until the next pointer is set */

while (!(next = READ ONCE(node->next)))

cpu relax();

/* Pass lock to next waiter. */

arch mcs spin unlock contended(&next->locked);

kernel/locking/mcs spinlock.h

92,0-1

```

Cache coherence only happens for the next core (will not be spinning; will enter critical section)

```

static inline

void mcs spin unlock(struct mcs spinlock **lock, struct mcs spinlock *node)

struct mcs_spinlock *next = READ_ONCE(node->next);

if (likely(!next)) {

* Release the lock by setting it to NULL

if (likely(cmpxchg release(lock, node, NULL) == node))

return;

/* Wait until the next pointer is set */

while (!(next = READ ONCE(node->next)))

cpu relax();

/* Pass lock to next waiter. */

arch mcs spin unlock contended(&next->locked);

kernel/locking/mcs spinlock.h

```

```

static inline

void mcs spin unlock(struct mcs spinlock **lock, struct mcs spinlock *node)

struct mcs_spinlock *next = READ_ONCE(node->next);

if (likely(!next)) {

* Release the lock by setting it to NULL

if (likely(cmpxchg release(lock, node, NULL) == node))

return;

/* Wait until the next pointer is set */

while (!(next = READ ONCE(node->next)))

cpu relax();

/* Pass lock to next waiter. */

arch mcs spin unlock contended(&next->locked);

kernel/locking/mcs spinlock.h

```

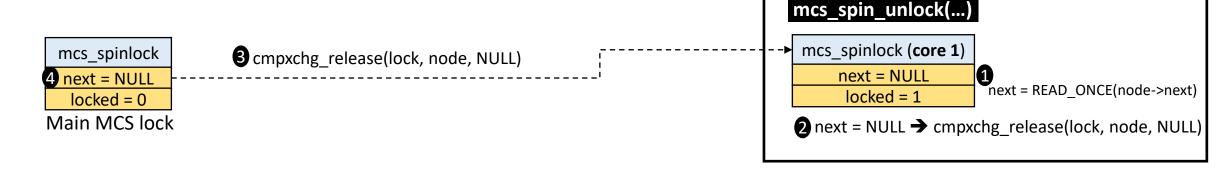

#### Ticket spinlock vs MCS lock

Figure 12: Performance of benchmarks using ticket locks and MCS locks.

#### **Benchmarks**

- FOPS: creates a single file and starts one process on each core. Repeated system calls "open() and close()".

- ✓ Executing the critical section increases from 450 cycles on two cores to 852 cycles on four cores

- ✓ The critical section is executed multiple times per-operation and modifies shared data, which incurs costly cache misses

- MEMPOP

- ✓ One process per core

- ✓ Each process mmaps 64 kB of memory with the MAP\_POPULATE flag, then munmaps the memory

- PFIND: searches for a file by executing several instances of the GNU find utility

- EXIM (mail server): A single master process

listens for incoming SMTP connections via TCP

and forks a new process for each connection

Reference Paper: Boyd-Wickizer, Silas, et al. "Non-scalable locks are dangerous." Proceedings of the Linux Symposium. 2012.

#### MCS Lock History in Linux Kernel

- Two variants

- ✓ Standard: v3.15

- ➤ None of Linux kernel subsystems uses it (No one calls mcs\_spin\_lock() and mcs\_spin\_unlock()) because:

struct mcs spinlock \*next;

cernel/locking/mcs spinlock.h

int locked; /\* 1 if lock acquired \*/

count; /\* nesting count, see gspinlock.c \*/

- sizeof(struct mcs spinlock) > 4

- Note: sizeof (msc spinlock struct) = 16

- spinlock struct is embedded into kernel structure. Example:

- □ struct page (size = 64) cannot tolerate the increased size

- > kernel/locking/mcs spinlock.h

- > Replacement of ticket spinlock: qspinlock based on standard MCS lock (v4.2)

- A simple generic 4-byte queued spinlock

- qspinlock is the default spinlock mechanism

- ✓ Cancelable MCS lock (OSQ Optimistic Spin Queue: MCS-like lock): v3.15

- > Used by mutex implementation & rw-semaphores

- ➤ Mutex implementation paths:

- Fastpath: Uncontended case by using cmpxchg()

- Midpath (optimistic spinning) The priority of the lock owner is the highest one

- ☐ Spin for mutex lock acquisition when the lock owner is running.

- ☐ The lock owner is likely to release the lock soon.

- Slowpath: The task is added to the waiting queue and sleeps until woken up by the unlock path.

- Mutex is a hybrid type (spinning & sleeping): Busy-waiting for a few cycles instead of immediately sleeping

- kernel/locking/{mutex.c, osq\_lock.c}

- ➤ Reference: Generic Mutex Subsystem

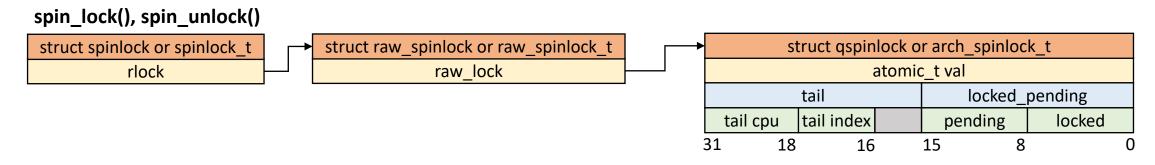

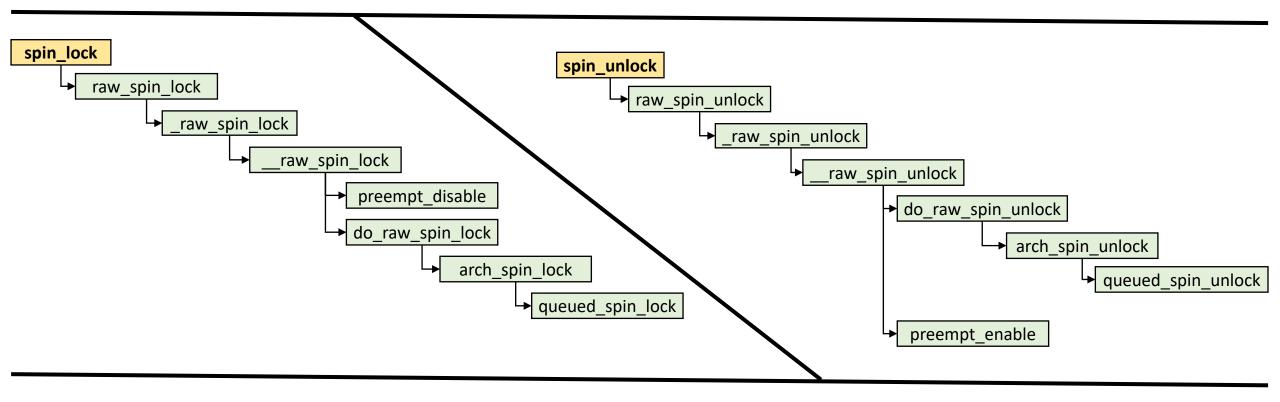

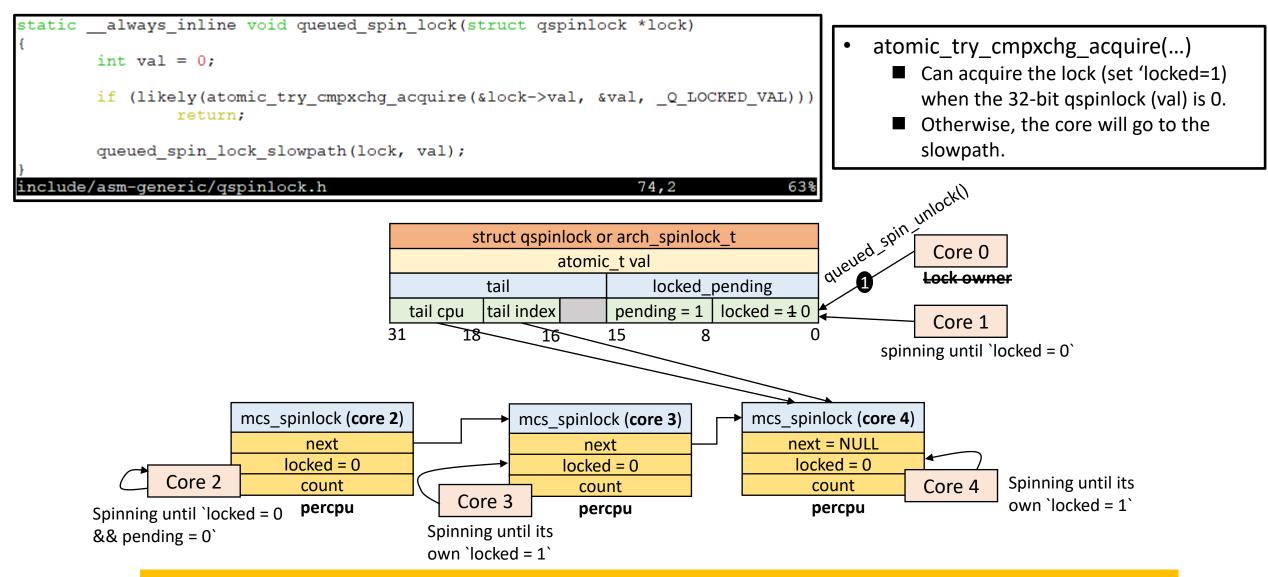

# qspinlock (Queue spinlock)

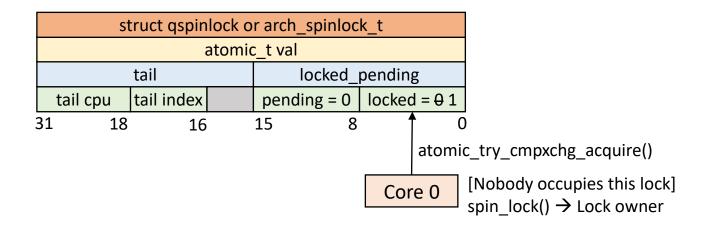

qspinlock (Queue spinlock) – First core to acquire the lock

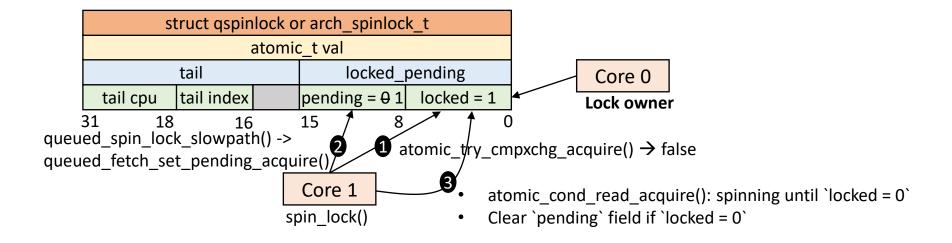

#### qspinlock – Second core to acquire the lock

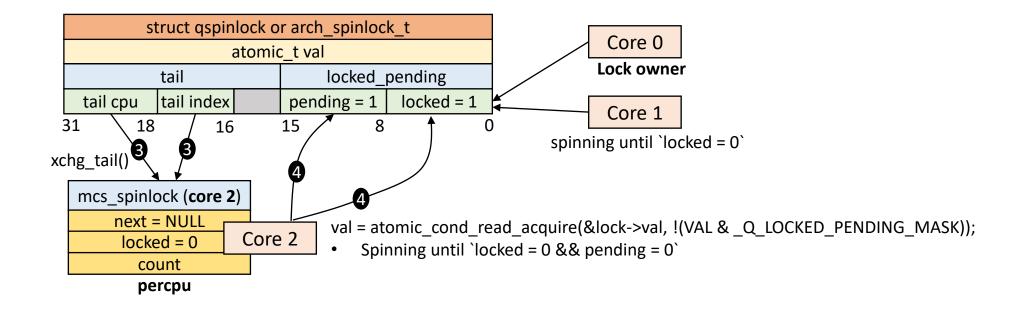

[Second core for lock acquisition] Spinning by checking `locked` field of arch\_spinlock\_t (Optimization: No need to configure a per-cpu MSC struct)

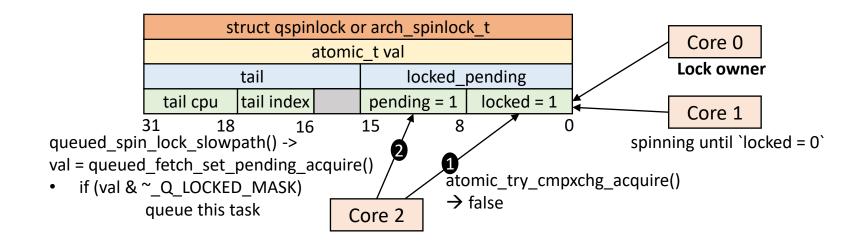

### qspinlock – Third core to acquire the lock

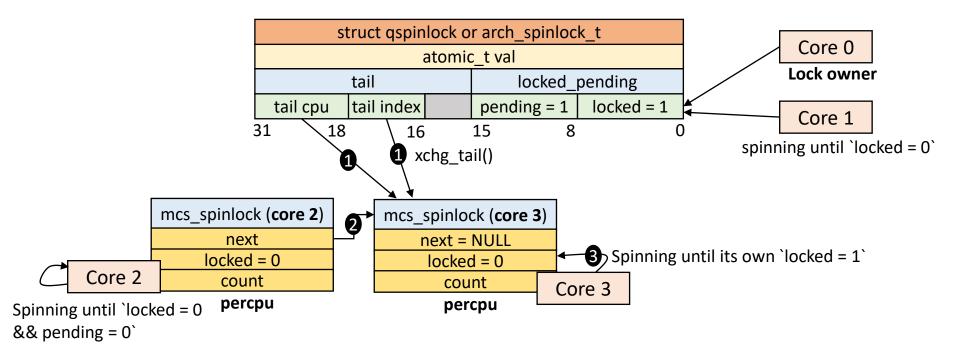

#### qspinlock – Third core to acquire the lock

### qspinlock – Forth core to acquire the lock

[Forth and later core: N >= 4] Spinning until its own `locked = 1`: Improve cache bouncing

Who sets `mcs\_spinlock.locked = 1`? (Hint: Adhere to MCS lock implementation)

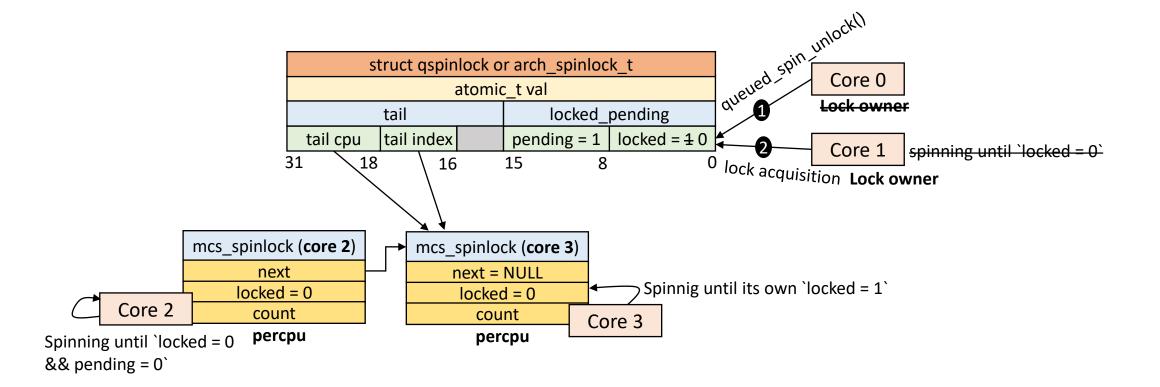

### qspinlock - queued\_spin\_unlock()

qspinlock - queued\_spin\_unlock() & queued\_spin\_lock()

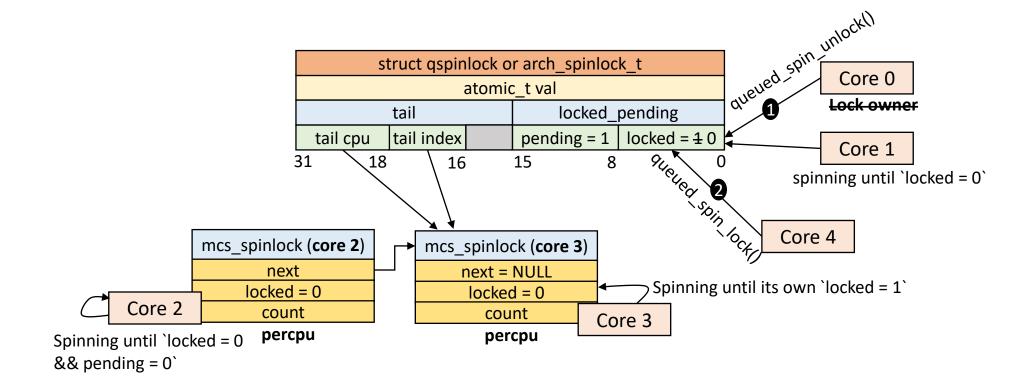

What happens to core 4 for invoking queued\_spin\_lock() under this circumstance?

### qspinlock - queued\_spin\_unlock() & queued\_spin\_lock()

- 1. Core 4 is queued: Adhere to the principle of ticket spinlock

- 2. Spin its own 'mcs\_spinlock.locked': Improve cache bouncing

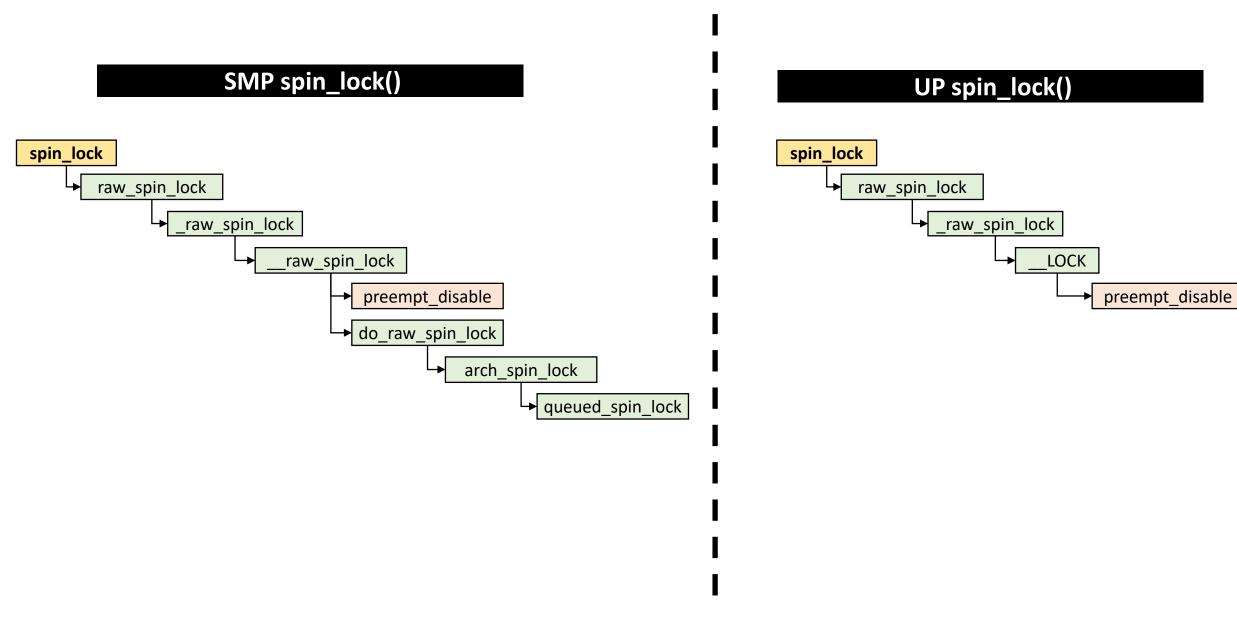

# spin\_lock() SMP & UP

# spinlock() variants

- spin\_lock() & spin\_unlock()

✓ Multiple process contexts share the same data

- spin\_lock\_irq() & spin\_unlock\_irq()

✓ Process context and top halve (hardirq) share the same data

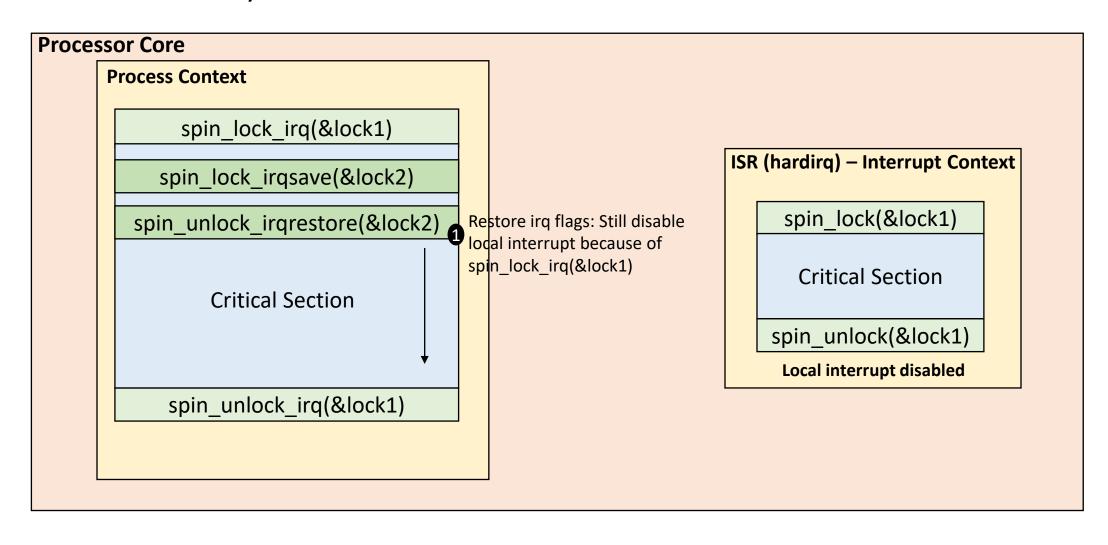

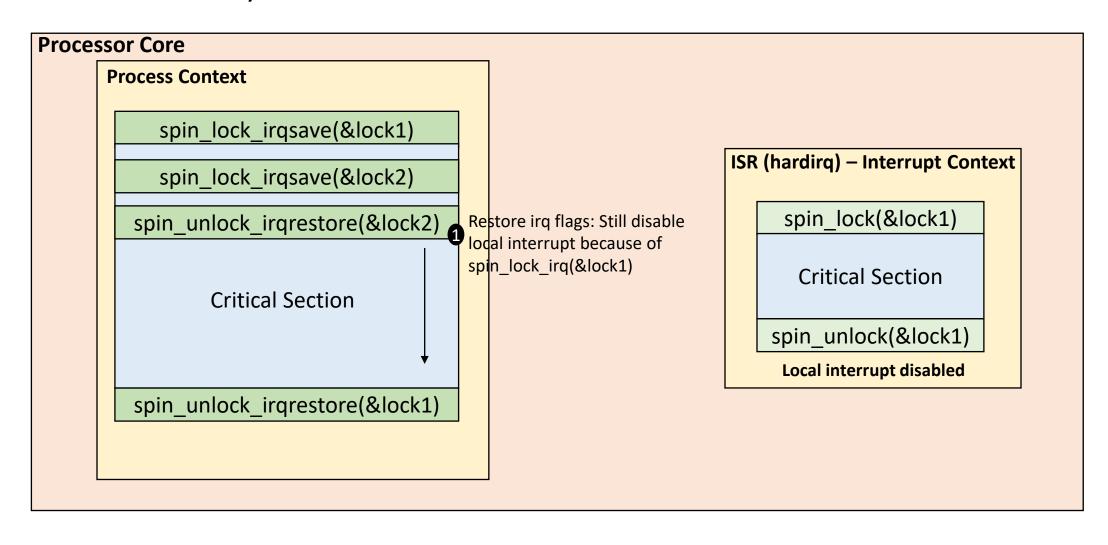

- spin\_lock\_irqsave() & raw\_spin\_unlock\_irqrestore()

- ✓ Process context and top halve (hardirg) share the same data

- ✓ Save/restore eflags

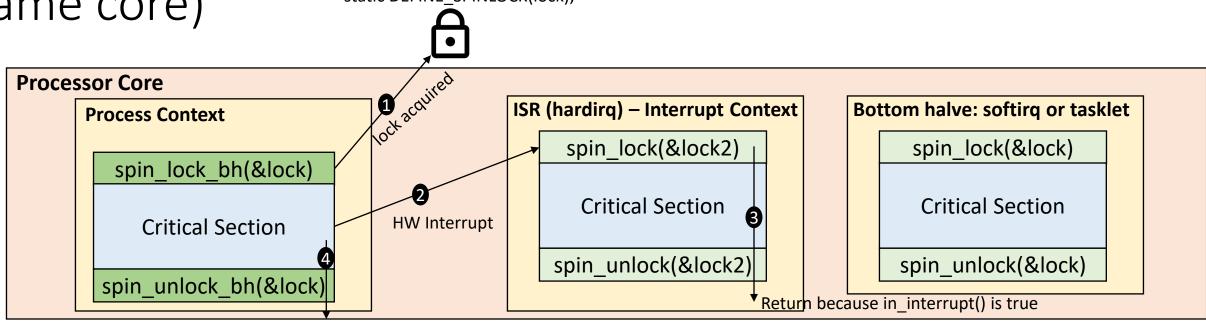

- spin\_lock\_bh() & spin\_unlock\_bh()

- ✓ Process context and bottom halve share the same data

- spin\_lock\_nest\_lock() & spin\_lock\_nested()

- ✓ lockdep: Annotate places where we take multiple locks of the same class and avoid deadlock Commit b7d39aff9145 ("lockdep: spin\_lock\_nest\_lock()")

# spinlock() variants

- spin\_lock() & spin\_unlock()

✓ Multiple process contexts share the same data

- spin\_lock\_irq() & spin\_unlock\_irq()

- ✓ Process context and top halve (hardirq) share the same data

- spin\_lock\_irqsave() & raw\_spin\_unlock\_irqrestore()

- ✓ Process context and top halve (hardirq) share the same data

- ✓ Save/restore eflags

- spin\_lock\_bh() & spin\_unlock\_bh()

- ✓ Process context and bottom halve share the same data

- spin\_lock\_nest\_lock() & spin\_lock\_nested()

- ✓ lockdep: Annotate places where we take multiple locks of the same class and avoid deadlock Commit b7d39aff9145 ("lockdep: spin\_lock\_nest\_lock()")

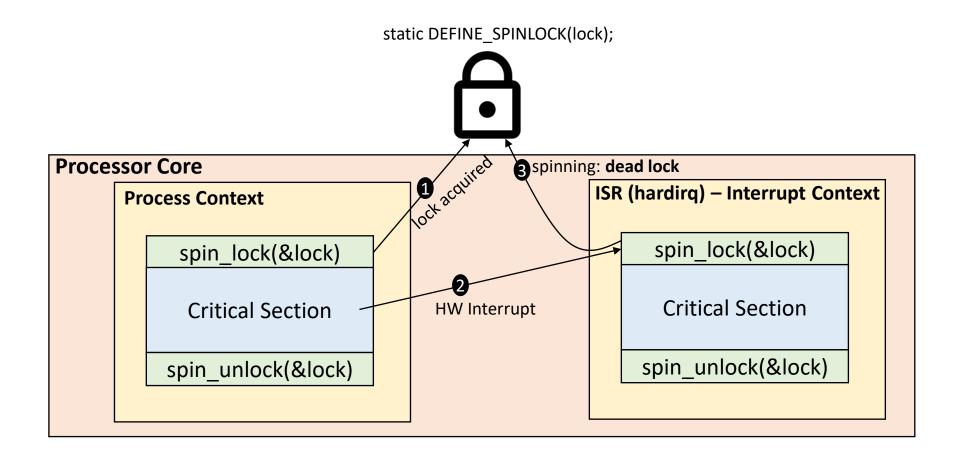

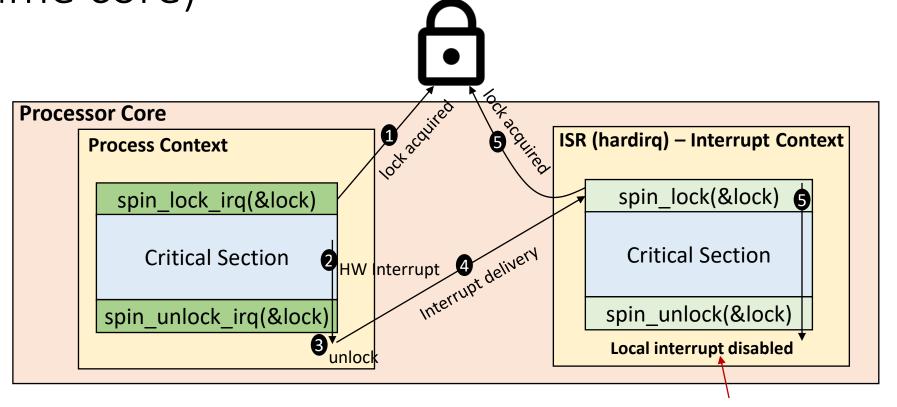

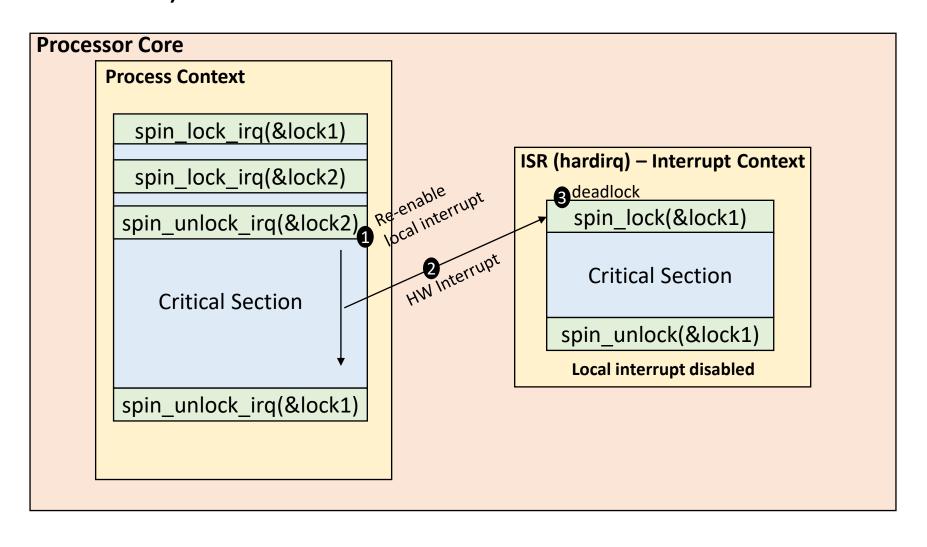

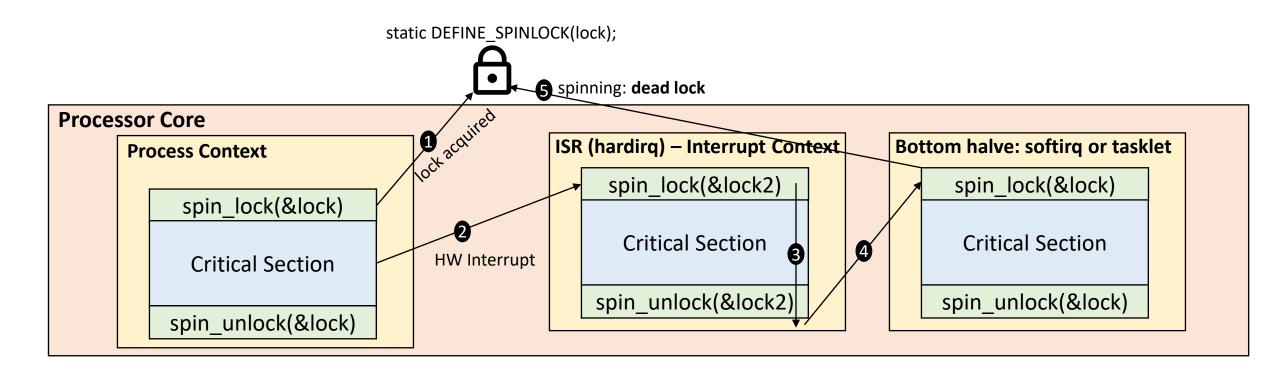

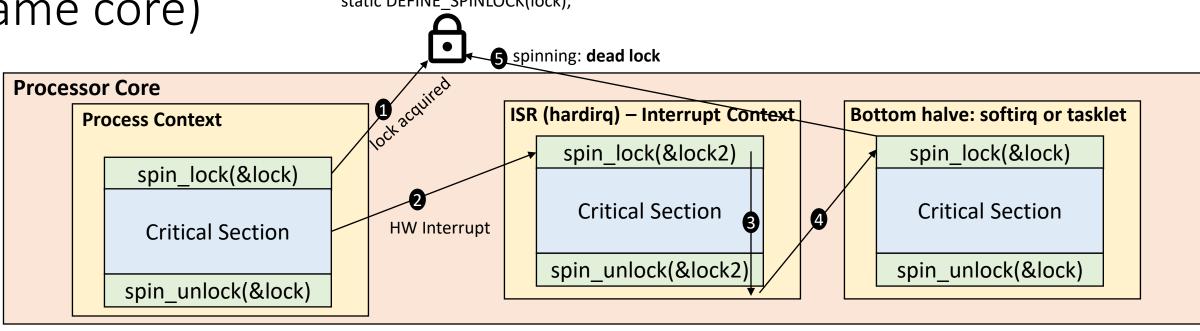

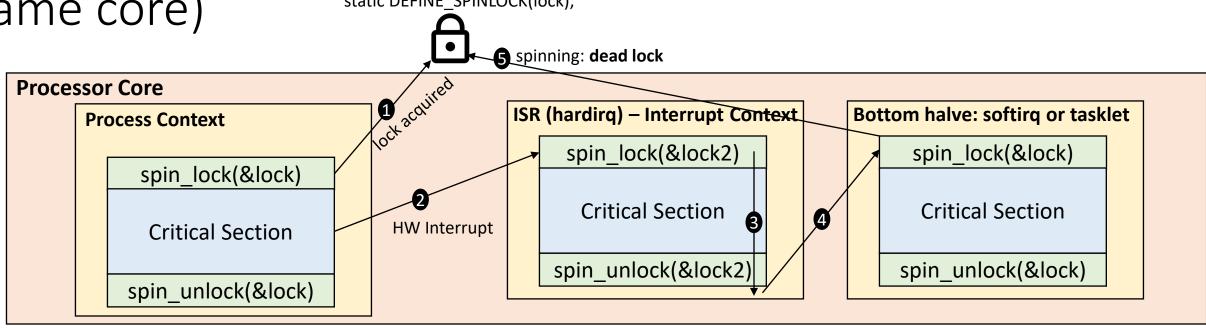

Deadlock between process context and interrupt context (the same core)

Deadlock only happens on the same core in this circumstance

Deadlock between process context and interrupt context (the same core)

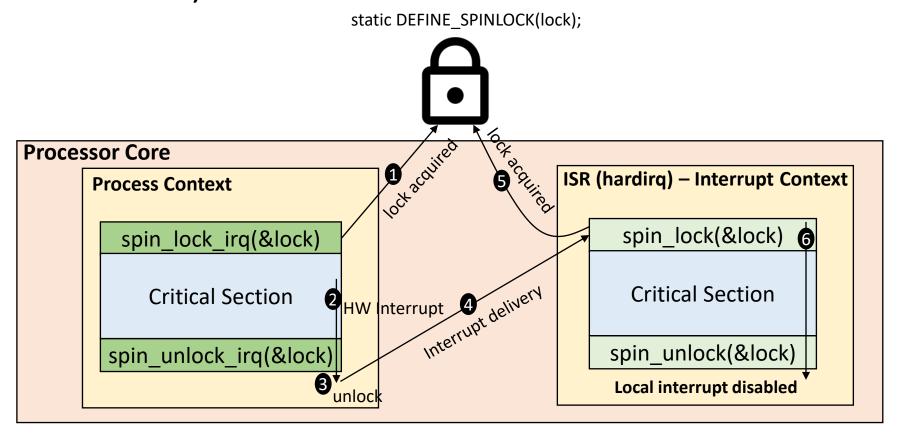

- Use spin\_{un}lock\_irq() or spin\_{un}lock\_irqsave() to prevent deadlock

- ✓ spin\_lock\_irq() or spin\_lock\_irqsave(): Disable local interrupt delivery

- ✓ spin\_unlock\_irq() or spin\_unlock\_irqsave(): Enable local interrupt delivery

Deadlock between process context and interrupt context (the same core)

static DEFINE\_SPINLOCK(lock);

Who disables the local interrupt before entering ISR?

- Linux kernel common interrupt code?

- CPU HW?

### common\_interrupt(): entry point for all normal device IRQs

```

/* Device interrupts common/spurious */

DECLARE IDTENTRY IRQ(X86 TRAP OTHER,

common interrupt);

#ifdef CONFIG X86 LOCAL APIC

DECLARE IDTENTRY IRQ(X86 TRAP OTHER,

spurious interrupt);

#endif

arch/x86/include/asm/idtentry.h

/* Entries for common/spurious (device) interrupts */

#define DECLARE IDTENTRY IRQ(vector, func)

idtentry irq vector func

arch/x86/include/asm/idtentry.h

.macro idtentry irg vector cfunc

.p2align CONFIG X86 L1 CACHE SHIFT

idtentry \vector asm \cfunc \cfunc has error code=1

endm

arch/x86/entry/entry 64.S

```

```

.macro idtentry vector asmsym cfunc has error code:rec

SYM CODE START(\asmsym) → SYM CODE START(asm common interrupt

UNWIND HINT IRET REGS offset=\has error code*8

ASM CLAC

.if \has error code == 0

pushq $-1

/* ORI

rt */

.endif

.if \vector == X86 TRAP BP

* If coming from kernel space, create

* int3 handler to emulate a call inst:

$3, CS-ORIG RAX(%rsp)

.Lfrom usermode no gap \@

jnz

.rept

5*8(%rsp)

pushq

.endr

UNWIND HINT IRET REGS offset=8

.Lfrom usermode no gap \0:

.endif

idtentry body \cfunc \has error code

ASM NOKPROBE (\asmsym)

SYM CODE END(\asmsym)

endm

arch/x86/entry/entry 64.S

```

```

.macro idtentry vector asmsym cfunc has error code:req

.macro idtentry body cfunc has error code:req

SYM CODE START (\asmsym) → SYM CODE START(asm common interrupt

call

error entry

UNWIND HINT IRET REGS offset=\has error code*8

UNWIND HINT REGS

ASM CLAC

%rsp, %rdi

/* pt regs pointer into 1st argu

movq

.if \has error code == 0

ment*/

pusha $-1

/* ORI

.if \has error code == 1

rt */

ORIG RAX(%rsp), %rsi

/* get error code into 2nd argum

.endif

ent*/

$-1, ORIG RAX(%rsp)

/* no syscall to restart */

.if \vector == X86 TRAP BP

.endif

\cfunc

call

* If coming from kernel space, create

* int3 handler to emulate a call inst

qmp

error return

.endm

$3, CS-ORIG RAX(%rsp)

testb

.Lfrom usermode no gap \@

jnz

arch/x86/entry/entry 64.S

320,18

.rept

5*8(%rsp)

pushq

.endr

$ objdump -D out/obj/linux/vmlinux

UNWIND HINT IRET REGS offset=8

.Lfrom usermode no gap \0:

fffffffff81400b00 <asm common interrupt>:

.endif

ffffffff81400b00:

e8 fb 03 00 00

callq ffffffff81400f00 <error entry>

48 89 e7

%rsp,%rdi

ffffffff81400b05:

mov

48 8b 74 24 78

0x78(%rsp),%rsi

ffffffff81400b08:

mov

idtentry body \cfunc \has error code

fffffffff81400b0d:

48 c7 44 24 78 ff ff

$0xfffffffffffffff,0x78(%rsp)

movq

ffffffff81400b14:

ff ff

ASM NOKPROBE (\asmsym)

ffffffff81400b16:

e8 65 b0 f6 ff

callq ffffffff8136bb80 <common interrupt>

SYM CODE END(\asmsym)

fffffffff81400ff0 <error return>

ffffffff81400b1b:

e9 d0 04 00 00

.endm

data16 nopw %cs:0x0(%rax,%rax,1)

ffffffff81400b20:

66 66 2e 0f 1f 84 00

ffffffff81400b27:

00 00 00 00

data16 nopw %cs:0x0(%rax,%rax,1)

arch/x86/entry/entry 64.S

ffffffff81400b2b:

66 66 2e 0f 1f 84 00

00 00 00 00

ffffffff81400b36:

66 2e 0f 1f 84 00 00

mopw

%cs:0x0(%rax,%rax,1)

ffffffff81400b3d:

00 00 00

```

```

$ objdump -D out/obj/linux/vmlinux

ffffffff81400b00 <asm common interrupt>:

callq ffffffff81400f00 <error entry>

e8 fb 03 00 00

48 89 e7

ffffffff81400b05:

%rsp,%rdi

48 8b 74 24 78

ffffffff81400b08:

0x78 (%rsp), %rsi

mov

$0xffffffffffffffff, 0x78 (%rsp)

ffffffff81400b0d:

48 c7 44 24 78 ff ff

movq

e8 65 b0 f6 ff

callq ffffffff8136bb80 <common interrupt>

ffffffff81400b16:

ffffffff81400b1b:

e9 d0 04 00 00

pami

ffffffff81400ff0 <error return>

66 66 2e 0f 1f 84 00

data16 nopw %cs:0x0(%rax,%rax,1)

00 00 00 00

ffffffff81400b27:

data16 nopw %cs:0x0(%rax, %rax,1)

66 66 2e 0f 1f 84 00

ffffffff81400b2b:

00 00 00 00

%cs:0x0(%rax,%rax,1)

ffffffff81400b36:

66 2e 0f 1f 84 00 00

nopw

ffffffff81400b3d:

00 00 00

```

```

(gdb) bt 3

#0 0xfffffffff81400b00 in asm common interrupt ()

0xffffffff813764d5 in native restore fl (flags=582) at /home/adrian/git-repo

gdb-linux-real-mode/src/linux-5.11/arch/x86/include/asm/irgflags.h:84/

(More stack frames follow...)

(qdb) info b

Disp Enb Address

Num

Type

What

breakpoint

0xffffffff81400b00 <asm common interrupt>

keep y

breakpoint already hit 1 time

breakpoint

Oxffffffff8136bb80 in common interrupt at /home/

adrian/git-repo/gdb-linux-real-mode/src/linux-5.11/arch/x86/kernel/irg.c:239

(qdb) info registers eflags

eflags

[ IOPL=0 ZF PF ] ← IF (Interrupt Enable Flag) is disabled!

0 \times 46

```

The current stack is not switched yet: will be done in error entry()

Local interrupt has been disabled before entering asm\_common\_interrupt(): CPU disables it.

```

$ objdump -D out/obj/linux/vmlinux

fffffffff81400b00 <asm common interrupt>:

e8 fb 03 00 00

callq fffffffff81400f00 <error entry>

ffffffff81400b00:

48 89 e7

ffffffff81400b05:

%rsp,%rdi

mov

0x78(%rsp),%rsi

ffffffff81400b08:

48 8b 74 24 78

mov

$0xffffffffffffffff, 0x78 (%rsp)

fffffffff81400b0d:

48 c7 44 24 78 ff ff

movq

ffffffff81400b14:

ff ff

callg ffffffff8136bb80 <common interrupt>

ffffffff81400b16:

e8 65 b0 f6 ff

e9 d0 04 00 00

jmpq

fffffffff81400ff0 <error return>

ffffffff81400b1b:

data16 nopw %cs:0x0(%rax,%rax,1)

66 66 2e 0f 1f 84 00

ffffffff81400b20:

00 00 00 00

ffffffff81400b27:

data16 nopw %cs:0x0(%rax,%rax,1)

ffffffff81400b2b:

66 66 2e 0f 1f 84 00

ffffffff81400b32:

00 00 00 00

66 2e 0f 1f 84 00 00

%cs:0x0(%rax,%rax,1)

ffffffff81400b36:

nopw

ffffffff81400b3d:

00 00 00

```

```

Thread 1 hit Breakpoint 2, common_interrupt (regs=0xffffffff81a03d88, error_code =48) at /home/adrian/git-repo/gdb-linux-real-mode/src/linux-5.11/arch/x86/kernel/irq.c:239

DEFINE_IDTENTRY_IRQ(common_interrupt)

(gdb) bt

#0 common_interrupt (regs=0xffffffff81a03d88, error_code=48) at /home/adrian/git-repo/gdb-linux-real-mode/src/linux-5.11/arch/x86/kernel/irq.c:239

#1 0xfffffff81400blb in asm_common_interrupt ()

#2 0x000000000000000000 in ?? ()

```

```

DEFINE_IDTENTRY_IRQ(common_interrupt)

{

struct pt_regs *old_regs = set_irq_regs(regs);

struct irq_desc *desc;

arch/x86/kernel/irq.c

```

```

#define DEFINE IDTENTRY IRQ(func)

static __always_inline void ##func(struct pt regs *regs, u8 vector);

visible noinstr void func(struct pt regs *regs,

common interrupt(...

unsigned long error code)

irqentry state t state = irqentry enter(regs);

instrumentation begin();

irq enter rcu();

kvm set cpu l1tf flush l1d();

##func (regs, (u8)error code);

irq exit rcu();

instrumentation end();

irqentry exit(regs, state);

__common_interrupt(...)

always inline void ##func(struct pt regs *regs, u8 vector)

arch/x86/include/asm/idtentry.h

182,1

```

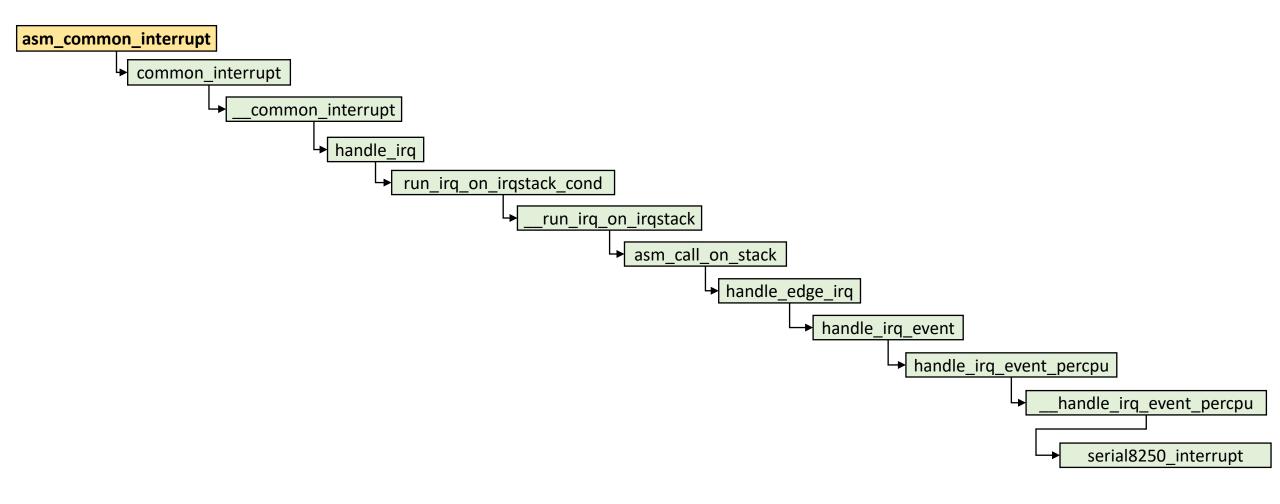

### **Common Interrupt Call Path: Serial Driver**

Common interrupt in Linux kernel: Handle vector number 32-255

## Common Interrupt Code Path

```

(qdb) bt

#0 serial8250 interrupt (irq=4, dev id=0xffff888240d52780) at /home/adrian/git-

repo/gdb-linux-real-mode/src/linux-5.11/include/linux/spinlock.h:354

#1 0xffffffff810822e0 in handle irg event percpu (desc=desc@entry=0xffff88810

004fa00, flags=flags@entry=0xffffc90000003f9c) at /home/adrian/git-repo/gdb-linu

x-real-mode/src/linux-5.11/kernel/irg/handle.c:156

#2 0xffffffff8108236f in handle irg event percpu (desc=desc@entry=0xffff8881000

4fa00) at /home/adrian/git-repo/gdb-linux-real-mode/src/linux-5.11/kernel/irg/ha

ndle.c:196

#3 0xffffffff810823d7 in handle irq event (desc=desc@entry=0xffff88810004fa00)

at /home/adrian/git-repo/gdb-linux-real-mode/src/linux-5.11/kernel/irg/handle.c:

213

#4 0xffffffff81085ee5 in handle edge irg (desc=0xffff88810004fa00) at /home/adr

ian/git-repo/gdb-linux-real-mode/src/linux-5.11/kernel/irg/chip.c:819

#5 0xffffffff81400ddf in asm call on stack () at /home/adrian/git-repo/gdb-linu

x-real-mode/src/linux-5.11/drivers/tty/serial/8250/8250 core.c:842

#6 0xffffffff8136bc38 in run irq on irqstack (desc=0xffff88810004fa00, func=<

optimized out>) at /home/adrian/git-repo/gdb-linux-real-mode/src/linux-5.11/arch

/x86/include/asm/irg stack.h:48

#7 run irg on irgstack cond (regs=0xffffc900018a3a78, desc=0xffff88810004fa00,

func=<optimized out>) at /home/adrian/git-repo/gdb-linux-real-mode/src/linux-5.1

1/arch/x86/include/asm/irq stack.h:101

#8 handle irg (regs=0xffffc900018a3a78, desc=0xffff88810004fa00) at /home/adria

n/git-repo/gdb-linux-real-mode/src/linux-5.11/arch/x86/kernel/irg.c:230

#9 common interrupt (vector=36 '$', regs=0xffffc900018a3a78) at /home/adrian/

git-repo/gdb-linux-real-mode/src/linux-5.11/arch/x86/kernel/irg.c:249

#10 common interrupt (regs=0xffffc900018a3a78, error code=36) at /home/adrian/gi

t-repo/gdb-linux-real-mode/src/linux-5.11/arch/x86/kernel/irg.c:239

#11 0xfffffffff81400b1b in asm common interrupt () at /home/adrian/git-repo/gdb-1

inux-real-mode/src/linux-5.11/drivers/tty/serial/8250/8250 core.c:842

#12 0x0000000000000000 in ?? ()

```

# CPU disables local interrupt if the interrupt handle is called via an interrupt gate

### 6.5.1 Call and Return Operation for Interrupt or Exception Handling Procedures

A call to an interrupt or exception handler procedure is similar to a procedure call to another protection level (see Section 6.4.6, "CALL and RET Operation Between Privilege Levels"). Here, the vector references one of two kinds of gates in the IDT: an **interrupt gate** or a **trap gate**. Interrupt and trap gates are similar to call gates in that they provide the following information:

- Access rights information

- The segment selector for the code segment that contains the handler procedure

- An offset into the code segment to the first instruction of the handler procedure

The difference between an interrupt gate and a trap gate is as follows. If an interrupt or exception handler is called through an interrupt gate, the processor clears the interrupt enable (IF) flag in the EFLAGS register to prevent subsequent interrupts from interfering with the execution of the handler. When a handler is called through a trap gate, the state of the IF flag is not changed.

Deadlock between process context and interrupt context (the same core)

# Deadlock between process context and interrupt context (the same core) – Solution 1

# Deadlock between process context and interrupt context (the same core) – Solution 2

# spinlock() variants

- spin\_lock() & spin\_unlock()

✓ Multiple process contexts share the same data

- spin\_lock\_irq() & spin\_unlock\_irq()

✓ Process context and top halve (hardirq) share the same data

- spin\_lock\_irqsave() & raw\_spin\_unlock\_irqrestore()

✓ Process context and top halve (hardirq) share the same data

- ✓ Save/restore eflags

- spin\_lock\_bh() & spin\_unlock\_bh()

- ✓ Process context and bottom halve share the same data

- spin\_lock\_nest\_lock() & spin\_lock\_nested()

- ✓ lockdep: Annotate places where we take multiple locks of the same class and avoid deadlock Commit b7d39aff9145 ("lockdep: spin\_lock\_nest\_lock()")

Deadlock between process context and bottom halve (the same core)

Deadlock between process context and bottom halve (the same core)

static DEFINE\_SPINLOCK(lock);

#### Bottom halve is invoked when returning from ISR

```

adrian@adrian-ubuntu:linux-5.11$ grep -r __ARCH_IRQ_EXIT_IRQS_DISABLED kernel/softirq.c:#ifndef __ARCH_IRQ_EXIT_IRQS_DISABLED arch/arm64/include/asm/hardirq.h:#define __ARCH_IRQ_EXIT_IRQS_DISABLED 1 arch/um/include/asm/hardirq.h:#define __ARCH_IRQ_EXIT_IRQS_DISABLED 1 arch/arm/include/asm/hardirq.h:#define __ARCH_IRQ_EXIT_IRQS_DISABLED 1 arch/powerpc/include/asm/hardirq.h:#define __ARCH_IRQ_EXIT_IRQS_DISABLED arch/s390/include/asm/hardirq.h:#define __ARCH_IRQ_EXIT_IRQS_DISABLED

```

Deadlock between process context and bottom halve (the same core)

static DEFINE\_SPINLOCK(lock);

### Softirg is invoked when returning from ISR

#### Softirq is invoked when running ksoftirqd

Deadlock between process context and bottom halve (the same core)

static DEFINE\_SPINLOCK(lock);

#### Softirg is invoked when returning from ISR

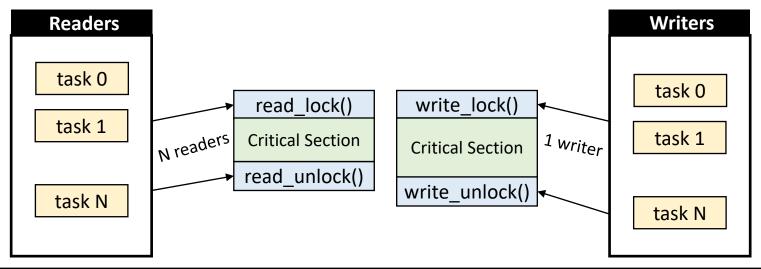

# rwlock (reader-writer spinlock)

- Concept

- ✓ [Without readers] Only one writer can enter CS

- ✓ [Without writer] N-readers can enter CS simultaneously...

- ✓ Readers and writer can enter CS simultaneously

- ✓ Reader(s) in CS → The writer needs to wait (spinning).

- ✓ Writer in CS → Readers need to wait (spinning)

- Mutual exclusion between reader and writer

- Writer might be starved!

- Reader has higher priority than writer

- Useful scenario: search for linked list without changing the list

- ✓ Example: tasklist\_lock → \_\_cacheline\_aligned DEFINE\_RWLOCK(tasklist\_lock);

- Linux kernel developers are trying to remove rwlock in most cases.

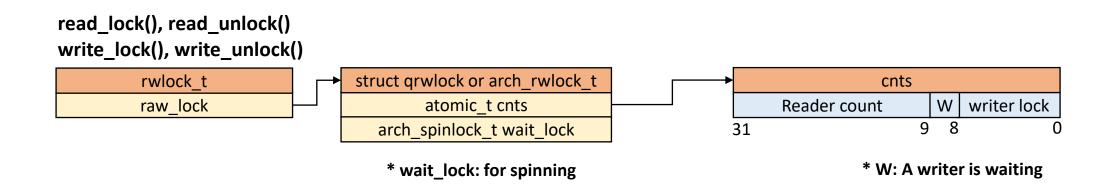

## rwlock (reader-writer spinlock): Data structure

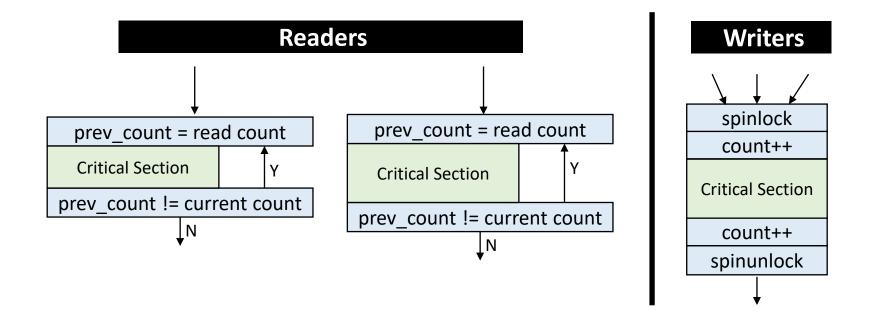

# seqlock (Sequential lock)

- Lockless readers (only retry loop)

- No writer starvation

- ✓ Writer has higher priority than reader

- ✓ No mutual exclusion between reader and writer

- Mutual exclusion between writers because of writers' spinlock

- Scenario: lots of readers and few writers

- ✓ Example: jiffies → Check get\_jiffies\_64(), tick\_setup\_periodic() and so on.

# spinlock derivative

|           | spinlock | rwlock | seqlock |

|-----------|----------|--------|---------|

| Reader(s) | 1        | N      | N       |

| Writer(s) | 1        | 1      | 1       |

# spinlock derivative and RCU

|           | spinlock | rwlock | seqlock | RCU |

|-----------|----------|--------|---------|-----|

| Reader(s) | 1        | N      | N       | N   |

| Writer(s) | 1        | 1      | 1       | 1   |

### Reference

- Boyd-Wickizer, Silas, et al. "Non-scalable locks are dangerous." Proceedings of the Linux Symposium. 2012. <a href="http://pdos.csail.mit.edu/papers/linux:lock.pdf">http://pdos.csail.mit.edu/papers/linux:lock.pdf</a>

- T. E. Anderson, "The performance of spin lock alternatives for shared-money multiprocessors", IEEE Transactions on Parallel and Distributed Systems, vol. 1, no. 1, pp. 6-16, 1990.

- J. M. Mellor-Crummey and M. L. Scott. "Algorithms for scalable synchronization on shared-memory multiprocessors", ACM Transactions on Computer Systems, 9(1):21–65, 1991.

- MCS locks and qspinlocks, LWN

- Is Parallel Programming Hard, And, If So, What Can You Do About It?